Good podcast? Give it some love!

Francesco Richichi

Five Minute VHDL Podcast

Good podcast? Give it some love!

Rate Podcast

Episodes of Five Minute VHDL Podcast

Mark All

Search Episodes...

How I can parallelize a RAM in FPGAhttps://surf-vhdl.com/how-to-implement-a-multi-port-memory-on-fpga/Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/francesco

Learn how to optimize a multiplier in particular cases:For a technical analysis go to the post:https://surf-vhdl.link/OptimizationVhdl12b25Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: podcast@surf-vhd

Link to the post:https://surf-vhdl.link/99990Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/francesco_surfvhdlTeachable courseshttps://surf-vhdl.link/coursesM

In this podcast we will understand how to connect a clock signal to our FPGAWebsitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/francesco_surfvhdlTeachable courses

What is dithering? Where we can use this technique?Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/francesco_surfvhdlTeachable courseshttps://surf-vhdl.link/co

VHDL GenericWebsitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/francesco_surfvhdlTeachable courseshttps://surf-vhdl.link/coursesMusic by Francis Preve - https://w

Even if the VHDL is not a software language, we can find a tyoica SW statement, the iterative statement. Let’s see how to use thishttps://t.me/SurfVhdl/92Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: p

Let’s understand how to implement a conditional statement in VHDLimage for the episodehttp://t.me/SurfVhdl/86Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/fr

Wait Statements in VHDLReference to pictures:https://t.me/SurfVhdl/82Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/francesco_surfvhdlTeachable courseshttps:/

Q&A#07- What is the first thing that a recruiter does?When a recruiter needs to hire you as VHDL expert, what do you think he or she will do to understand if you are good for him or her?What can you do in order to result a VHDL user?Let’s see i

And now is time to introduce formally a Processlink to the imageshttps://t.me/SurfVhdl/78Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/francesco_surfvhdlTeac

I receiver a question from Sandip. He got my reference, from my post on DDS.The question is:“I want to generate Square of 999kHz, 1000kHz and 1001kHzin VHDL Language and that would be implemented on a Zynq ZC702 evaluation board.Is it possible

VHDL Packageshttp://t.me/SurfVhdl/74Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/francesco_surfvhdlTeachable courseshttps://surf-vhdl.link/coursesMusic by F

After signal introduction, let's view what are the remaining VHDL objectsImages https://t.me/SurfVhdl/72Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/frances

I received a question from Haitham. He have to connect a computer to an FPGA using USB connection in order to transfer data from FPGA to the PC. Haitham is following my VHDL course “Start Learning VHDL Using FPGA”. In this course the last LAB i

In this Q&A episode I want to answer to the question on what is the VHLD design flowTo better follow the episode, see the picture on the telegram channelhttps://t.me/SurfVhdl/65Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYo

Introducing Flip-Flop in VHDLLink to the picture in the telegram channelhttps://t.me/SurfVhdl/61Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/francesco_surfv

This is the question many of you ask me very oftenI wish to give you some hint and a test bench template I use in my VHDL designs Here the link to the test bench template: https://t.me/SurfVhdl/58Websitehttps://surf-vhdl.comTelegram channelht

A brief overview to setup a ModelSim simulation environmentLink to the episode#12 picturet.me/SurfVhdl/53Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/france

Introduce signal in VHDL, what is a signal and how to use it.Image relative to this episodeWebsitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/francesco_surfvhdlTe

Solving a dispute in VHDL: the resolution functionLink to image for the episode#10Solving a dispute in VHDL: the resolution functiont.me/SurfVhdl/50Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: podcast

What is a driver in VHDL?Images for the episodet.me/SurfVhdl/46Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/francesco_surfvhdlTeachable courseshttps://surf-

In this brief episode I want to answer a question from Klajdi on simulation of SPI controller using Vivado Websitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/fran

Answering to Prashant. He asked me this question “What do we have to give as an input for i_clk and i_addr?”relative to the post: https://surf-vhdl.com/how-to-generate-sine-samples-in-vhdl/Websitehttps://surf-vhdl.comTelegram channelhttps://t.m

In this episode we will introduce the Concurrency conceptWebsitehttps://surf-vhdl.comTelegram channelhttps://t.me/SurfVhdlYou can contact memail: [email protected]: https://t.me/francesco_surfvhdlTeachable courseshttps://surf-vhdl.l

Join Podchaser to...

- Rate podcasts and episodes

- Follow podcasts and creators

- Create podcast and episode lists

- & much more

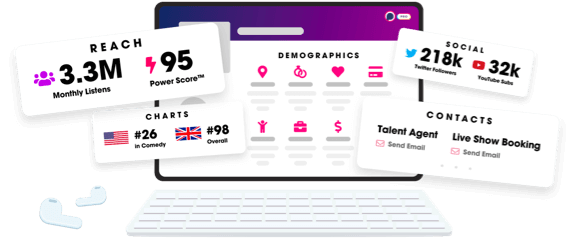

Unlock more with Podchaser Pro

- Audience Insights

- Contact Information

- Demographics

- Charts

- Sponsor History

- and More!

- Account

- Register

- Log In

- Find Friends

- Resources

- Help Center

- Blog

- API

Podchaser is the ultimate destination for podcast data, search, and discovery. Learn More

- © 2024 Podchaser, Inc.

- Privacy Policy

- Terms of Service

- Contact Us